今天台积电技术论坛上,2024年3月升任共同营运长,现任台积电业务开发、海外营运办公室资深副总暨副共同营运长的张晓强现场金句连发:

- 台积电做系统整合超过20年,领先推出CoWoS技术,我相信在座各位都可以拼出C-o-W-o-S-.......有天我发现连电视台主播都会拼这个词,你要是没听过CoWoS,大概 是外星人了!

- 过阵子也不用我和Cliff上台来演讲了,create一个Avatar来讲就好!

- (现场张晓强show出一张PPT标志着Nvidia近代GPU产品采用台积电制程技术的性能成长曲线直线向上)他说:AI发展快速,Nvidia产品从V100采用N12、A100采用N7、H100采用N4,一直最新一代 Blackwell采用N4P制程+CoWoS封装让算力成长1000倍,这迅猛的长曲线让人想到了昨晚的Nvidia股价.......

- 台积电今日技术论坛中,现场含金量最高的一张图应该是3D Integrated HPC Technology platform for AI。 张晓强说这张图是“Money Sheet”(既然价值连城,就不在此大放送!其实是因为现场是禁止摄影)从现场的图上看,是一款用于HPC和AI的新封装平台,并 以矽光子来改善互联。 他表示矽光子技术已经量产,只是这是第一次引入HPC中,用在Data Center。

- 如果有人要写台积电历史,一定要提到7nm,这是台积电第一次提供全世界最先进的技术,在此之前都是IDM。 之后台积电在2020年更领先进入5nm制程,2023年进入3nm制程。

以下是今日举行台湾场的技术论坛几个重点:

- AI将掀起第四次工业革命,2030年全世界将有10万个生成式AI机器人,生成式AI手机出货量将达2.4亿支。

- 为了满足AI运算需求,3D堆叠、先进封装技术越来越重要,未来几年将实现单晶片上整合超过2,000亿个电晶体并透过3D封装达到超过一兆个电晶体。

- 2024年3nm产能比2023年增加三倍,但还是不够用! !

- 2020~2024年,先进制程产能的年复合成长25%,特殊制程产能的复合成长率10%。 车用晶片出货复合成长率约50%。

- SOIC在2022~2026年的产能复合成长100%,CoWoS在2022~2026年的产能复合成长超过60%

- 台积电从2019年正式使用EUV设备,目前全球56%的EUV机台都在台积电。

- N3E已依计画在2023年第四季进入量产,客户的产品良率相当好。 台积电也开发出N3P技术,已通过验证,目前良率表现接近于N3E。 N3P已经收到了客户产品设计定案tape-outs,将于 2024 年下半年开始量产。

- 2nm是台积电第一次使用奈米片Nano-Sheet电晶体架构,目前进展非常顺利,NanoSheet奈米片的转换目标达90%,换成良率也超过80%,根据计画2nm是2025年下 半年量产。

- 针对制程后段,会导入新制程与材料,将电阻/电容延迟(RC delay)降低高达10%。 此外,为了强化功率传输,台积电也提供了超高性能金属/绝缘体/金属电容(SHPMIM),其容量密度是上一代技术的两倍之多。

- 台积电进入埃米(angstrom)时代的A16,结合2nm制程+超级电轨(Super Power Rail)架构设计。

- A16 技术的超级电轨(Super Power Rail)架构是一种创新的最佳晶圆背面供电网路解决方案。 A16 将供电网路移到晶圆背面而在晶圆正面释出更多讯号网路的布局空间,借以提升逻辑密度和效能。 此外,它还可以改善功率传输,并大幅减少IR 压降。再者,台积电的创新晶圆背面传输方案也是业界首创,保留了栅极密度与元件宽度的弹性,是具有复杂讯号布线及密集供电网路的HPC产品的最佳解决方案。 相较于台积公司的 N2P 制程,A16 在相同 Vdd (工作电压)下,速度增快8~10%; 在相同速度下,功耗降低15~20%,晶片密度提升高达 1.10X。 台积电计画在 2026 年下半年量产。

- NanoSheet奈米片电晶体的下一代会是互补式场效电晶体CFET架构,藉由不同材料的上下堆叠,让垂直堆叠的不同场效电晶体更靠近,改善电流且密度增加1.5~2倍。 台积电强调CFET不是纸上谈兵,研发已经成功验证在wafer siliocon上。

- 台积电指出,当电晶体架构从平面式(planer)发展到 FinFET,并即将转变至奈米片(nanosheet)架构之后,公司认为垂直堆叠的 nFET 和 pFET (即互补式场效电晶体CFET)是未来制程架构选项之一。台积电进一步指出,内部一直在积极研究将 CFET 用于未来制程架构的可能性。 在考量布线和制程复杂性后,CFET 密度将可提升 1.5 至 2X,除了 CFET,在低维材料方面取得了突破,也可实现进一步的尺寸和能源微缩。

- 再者,台积电也计画导入新的互连技术,以提升互连效能。 首先,对于铜互连技术,计画导入一个全新的通路结构(via scheme),进而将业界领先的通路电阻(via resistance)再降低 25%。 再者,计画采用一种全新的通路蚀刻停止层(via etch-stop-layer),可降低约6%的耦合电容。 还有,正在研发一种新的铜阻障方案(Cu barrier),可降低约 15%的铜线电阻。除铜互连外,台积电也在研发一种含有气隙的新型金属材料,可降低约 25%的耦合电容。 另外,嵌入石墨烯(Intercalated graphene)也是一种极具前景的新材料,可大幅缩短互连延迟。

- TSMC 3DFabricTM技术方面,包含三大平台:TSMC-SoIC、CoWoS和InFO。

- SoIC 平台:用于 3D 矽晶片堆叠,并提供 SoIC-P 和 SoIC-X 两种堆叠方案。 SoIC-P是一种微凸块堆叠解决方案,适用于讲求成本效益的应用如行动装置。 CoWoS 平台包括成熟度最高、采用矽中介层的 CoWoS-S,以及采用有机中介层的CoWoS-L 和 CoWoS-R。 InFO PoP 和 InFO-3D 适用于高阶行动式应用,InFO 2.5D 则适用于高效能运算的小晶片整合。 另外,根据产品需求,SoIC 晶片可与 CoWoS 或 InFO 整合。

- 适用于3D 小晶片堆叠技术的SoIC:SoIC-X 无凸块堆叠解决方案,无论是现有的9 微米键合间距前到后堆叠方案(front-to-back scheme),还是将于2027 年上市的 3 微米键合间距前到前堆叠方案(front-to-front scheme),裸晶到裸晶(die-to-die)互连密度均比40 微米到18 微米间距的微凸块前到前堆叠 方案高出10X 以上。 台积电的SoIC-X 技术非常适用于对效能要求极高的各类HPC应用。台积电更指出,看到客户对于 SoIC-X 技术的需求逐渐增加,预计到 2026 年底将会有 30 个客户设计定案tape-outs。

CoWoS 技术:可将先进的 SoC 或 SoIC 晶片与先进的高频宽记忆体HBM进行整合,满足AI 晶片的严苛要求。 台积电的SoIC 已透过 CoWoS-S 量产出货,并计画开发一种 8 倍光罩尺寸且具备采用A16 制程技术的 SoIC 晶片和 12 个HBM堆叠的 CoWoS 解决方案,计将在 2027 年开始量产。 直至今年年底,台积公司将为超过 25 个客户启动超过 150 个 CoWoS 客户产品设计定案tape-outs。

台积电与Nvidia合作推出Blackwell AI 加速器,是全球首款量产并将 2 个采用 5 奈米制程技术的 SoC 和 8 个HBM堆叠整合在一个模组中的 CoWoS-L 产品。

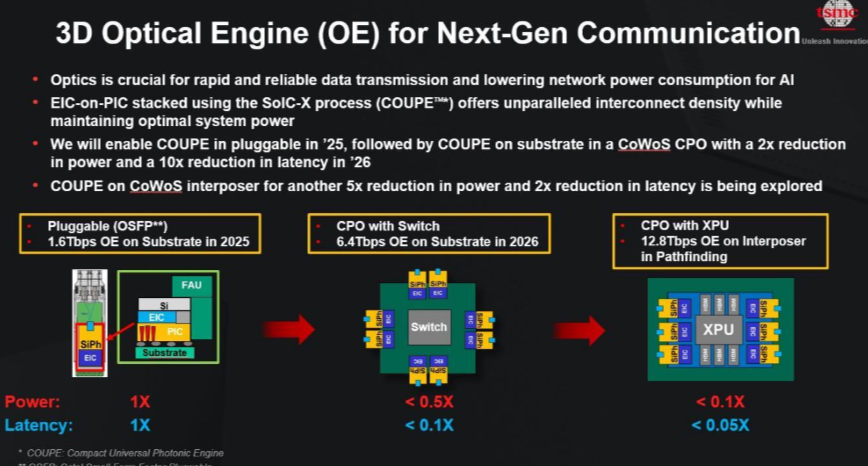

矽光子:台积电表示矽光子是共同封装光学元件CPO的最佳选择,因为其与半导体相容,且可与 EIC/PIC/交换器在封装层高度整合。 台积电创新的紧凑型通用光子引擎(COUPETM)技术透过最短路径的同质铜-铜介面整合电子积体电路(PIC)和光子积体电路(EIC),进而实现超高速射频(RF)讯号(200G/ λ)。

COUPE 解决方案可最小化使用面积,且具备光栅耦合器(GC)和边际耦合器(EC),可满足客户的各式需求。 台积电计画在 2025 年完成小型插拔式连接器的 COUPE 验证,2026 年将其整合于共同封装光学元件的 CoWoS 封装基板,借此可降低 2X 功耗、将延迟降低10X。

同时,台积电也探索一种更先进的共同封装光学元件方案,将 COUPE 整合于 CoWoS中介层,进而将功耗再降低 5X、将延迟再降低 2X。

相关新闻:

台积电魏哲家亲赴欧洲拜访ASML、德国蔡司,完成「摩尔定律续命」之旅

50%关税加上去,恐让中国成熟制程产能过剩更严重,「国产化」速度势必提前

中芯国际咬牙扩增28nm产能,杀价战与庞大折旧金额夹击