新思科技(Synopsys)宣布,推出业界首个完整的UCIe IP全面解决方案,每引脚运行速度高达40Gbps,以满足全球速度领先的人工智能数据中心对计算性能日益增长的要求,該40G UCIe IP将于 2024 年底推出,适用于多种晶圆代工厂及其工艺。

UCIe 互连是裸片到裸片连接的行业标准,对于多裸片封装中的高带宽、低延迟裸片到裸片连接至关重要,助力当下人工智能数据中心系统中的更多数据在异构和同构裸片或芯片组之间高效传输。

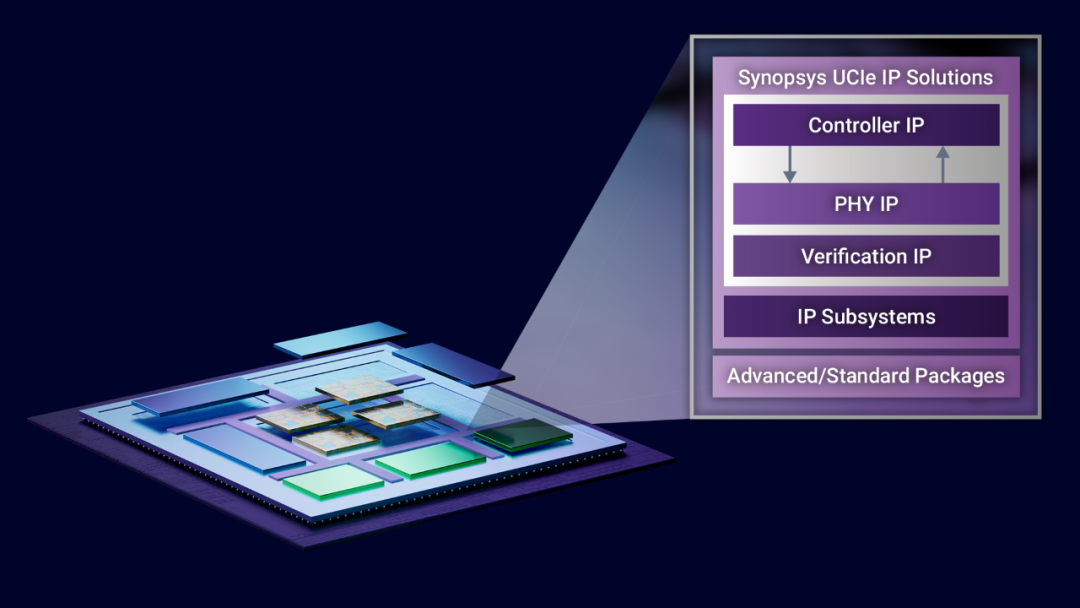

新思科技40G UCIe IP 支持有机基板和高密度先进封装技术,使开发者能够灵活地探索适合其需求的封装选项。新思的40G UCIe IP 完整解决方案包括了物理层、控制器和验证 IP,是新思科技全面、可扩展的多芯片系统设计解决方案的关键组成部分,可实现从早期架构探索到制造的快速异构集成。

新思科技 IP产品管理副总裁Michael Posner表示,新思科技发布业界首个完整的40G UCIe IP解决方案,彰显了新思对推动半导体创新领域的持续投入,也帮助新思科技的客户成功开发并优化面向性能人工智能计算系统的多芯片系统设计。

新思科技全新40G UCIe IP 解决方案的领先性能包括:

- 更简化的解决方案可简化IP集成:单参考时钟功能简化了时钟架构并优化了功耗。为便于使用和集成,该IP加快了裸片到裸片链路的初始化,无需加载固件。

- 芯片健康监测增强了多芯片系统封装的可靠性:为了确保芯片、裸片到裸片以及多芯片系统封装层面的可靠性,新思科技40G UCIe IP 提供了测试和芯片生命周期管理 (SLM) 功能。此外,监控、测试和修复 IP 以及集成信号完整性监控器可实现从设计到现场的多芯片系统封装诊断和分析。

- 成功的生态系统互操作性:针对当前全新 CPU 和 GPU 的片上互连需求,新思科技40GUCIe IP 支持业界广泛的芯片上互连结构,包括 AXI、CHI 芯片到芯片、streaming、PCI Express 和 CXL。

- 为了实现成功的互操作性,该 IP 符合 UCIe 1.1 和 2.0 标准,新思科技作为 UCIe 联盟的积极成员,协助推动开发和推广以上标准。

- 预验证的设计参考流程:新思科技UCIe IP与3DIC Compiler(一个统一的从探索到签收平台)的组合可用于新思科技的预验证设计参考流程,该流程包括所有必要的设计辅助工具,如自动布线流程、内插研究和信号完整性分析。

- 适用于多芯片系统设计的广泛 IP 解决方案:除了 UCIe IP 和高速 SerDes,新思科技还提供HBM3 和 3DIO IP,以实现大容量存储器和 3D 封装。